# **6th Generation Intel® Processor Datasheet for S-Platforms**

**Datasheet - Volume 2 of 2**

Supporting the 6th Generation Intel<sup>®</sup> Core<sup>™</sup> Processor and Intel<sup>®</sup> Pentium<sup>®</sup> Processor Families based on the S-Platform

February 2016

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document.

All information provided here is subject to change without notice. Contact your Intel representative to obtain the latest Intel product specifications and

The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or visit http:// www.intel.com/design/literature.htm.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Learn more at http://www.intel.com/ or from the OEM or retailer.

No computer system can be absolutely secure.

Intel® Hyper-Threading Technology (Intel® HT Technology) is available on select Intel® Core™ processors. It requires an Intel® HT Technology enabled system. Consult your PC manufacturer. Performance will vary depending on the specific hardware and software used. Not available on Intel® Core i5-750. For more information including details on which processors support Intel® HT Technology, visit http://www.intel.com/info/hyperthreading.

Intel® High Definition Audio (Intel® HD Audio) requires an Intel® HD Audio enabled system. Consult your PC manufacturer for more information. Sound quality will depend on equipment and actual implementation. For more information about Intel® HD Audio, refer to http://www.intel.com/

Intel® 64 architecture requires a system with a 64-bit enabled processor, chipset, BIOS and software. Performance will vary depending on the specific hardware and software you use. Consult your PC manufacturer for more information. For more information, visit http://www.intel.com content/www/us/en/architecture-and-technology/microarchitecture/intel-64-architecture-general.html.

Intel® Virtualization Technology (Intel® VT) requires a computer system with an enabled Intel® processor, BIOS, and virtual machine monitor (VMM). Functionality, performance or other benefits will vary depending on hardware and software configurations. Software applications may not be compatible with all operating systems. Consult your PC manufacturer. For more information, visit http://www.intel.com/go/virtualization

The original equipment manufacturer must provide TPM functionality, which requires a TPM-supported BIOS. TPM functionality must be initialized and may not be available in all countries.

For Enhanced Intel SpeedStep® Technology, see the Processor Spec Finder at http://ark.intel.com/ or contact your Intel representative for more

Intel® AES-NI requires a computer system with an AES-NI enabled processor, as well as non-Intel software to execute the instructions in the correct sequence. AES-NI is available on select Intel® processors. For availability, consult your reseller or system manufacturer. For more information, see http://software.intel.com/en-us/articles/intel-advanced-encryption-standard-instructions-aes-ni/

Intel® Active Management Technology (Intel® AMT) should be used by a knowledgeable IT administrator and requires enabled systems, software, activation, and connection to a corporate network. Intel AMT functionality on mobile systems may be limited in some situations. Your results will depend on your specific implementation. Learn more by visiting Intel® Active Management Technology.

No computer system can provide absolute security under all conditions. Intel® Trusted Execution Technology (Intel® TXT) requires a computer with Intel® Virtualization Technology, an Intel TXT-enabled processor, chipset, BIOS, Authenticated Code Modules and an Intel TXT-compatible measured launched environment (MLE). Intel TXT also requires the system to contain a TPM v1.s. For more information, visit http://www.intel.com/technology/

Requires a system with Intel® Turbo Boost Technology. Intel Turbo Boost Technology and Intel Turbo Boost Technology 2.0 are only available on select Intel® processors. Consult your PC manufacturer. Performance varies depending on hardware, software, and system configuration. For more information, visit https://www-ssl.intel.com/content/www/us/en/architecture-and-technology/turbo-book

Intel® Advanced Vector Extensions (Intel® AVX) are designed to achieve higher throughput to certain integer and floating point operations. Due to varying processor power characteristics, utilizing AVX instructions may cause a) some parts to operate at less than the rated frequency and b) some parts with Intel® Turbo Boost Technology 2.0 to not achieve any or maximum turbo frequencies. Performance varies depending on hardware, software, and system configuration and you should consult your system manufacturer for more information. Intel® Advanced Vector Extensions refers to Intel® AVX, Íntel® AVX2 or Intel® AVX-512. For more information on Intel® Turbo Boost Technology 2.0, visit https://www-ssl.intel.com/content/www/us/en/ architecture- and -technology/turbo-boost/turbo-boost-technology. html

Intel, Intel Core, Celeron, Pentium, Intel SpeedStep, and the Intel logo are trademarks of Intel Corporation in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others.

Copyright © 2015-2016, Intel Corporation, All rights reserved.

# **Contents**

| Revision History                                                    | 16 |

|---------------------------------------------------------------------|----|

| 1.0 Introduction                                                    | 17 |

| 2.0 Processor Configuration Register Definitions and Address Ranges | 18 |

| 2.1 Register Terminology                                            | 18 |

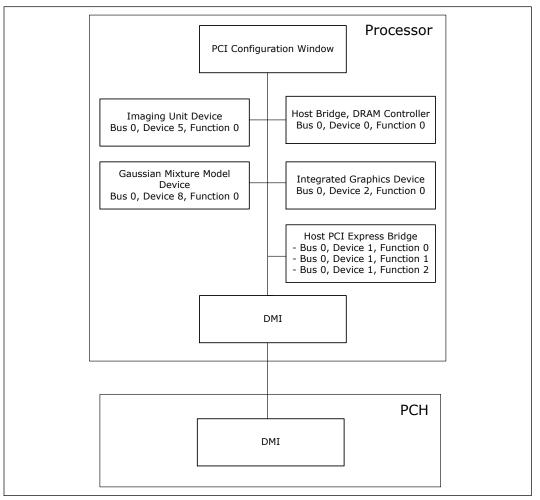

| 2.2 PCI Devices and Functions                                       | 19 |

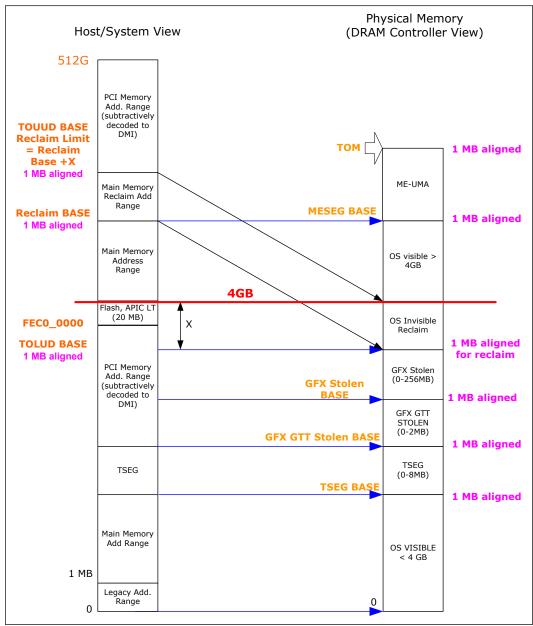

| 2.3 System Address Map                                              | 21 |

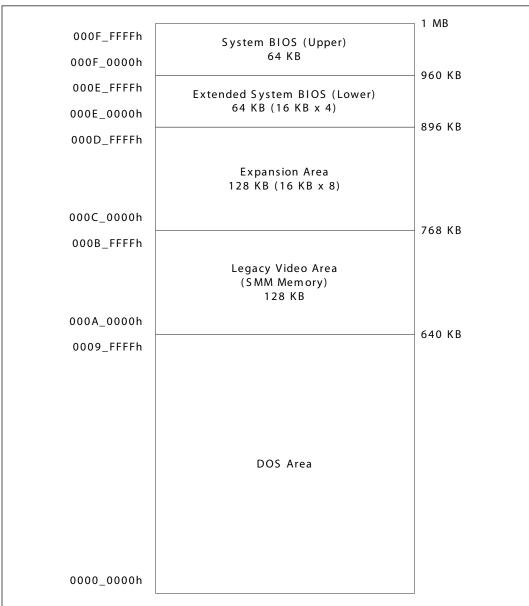

| 2.4 Legacy Address Range                                            |    |

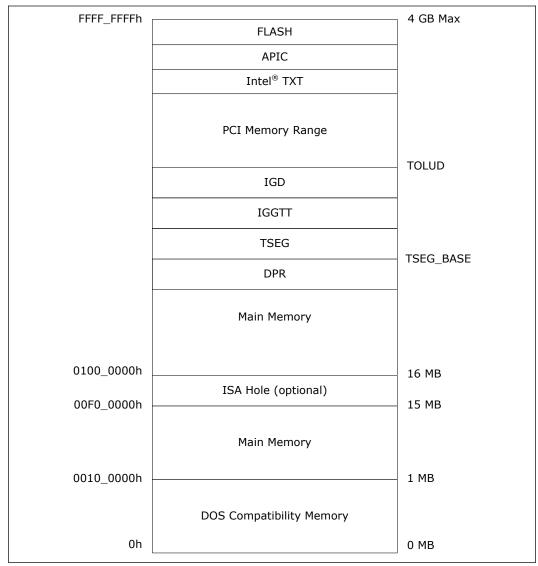

| 2.5 Main Memory Address Range (1 MB – TOLUD)                        | 27 |

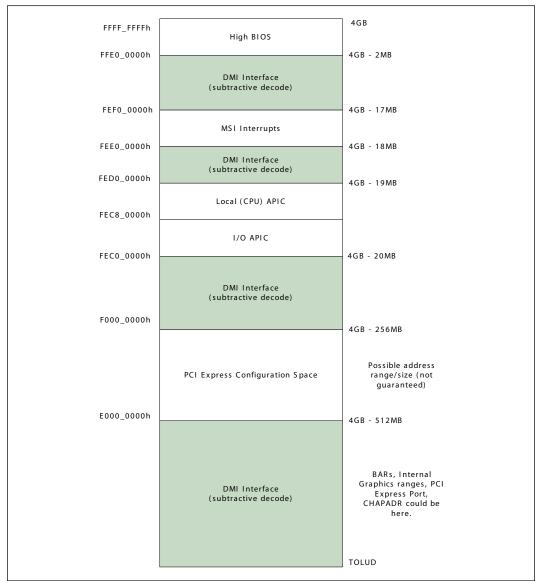

| 2.6 PCI Memory Address Range (TOLUD – 4 GB)                         |    |

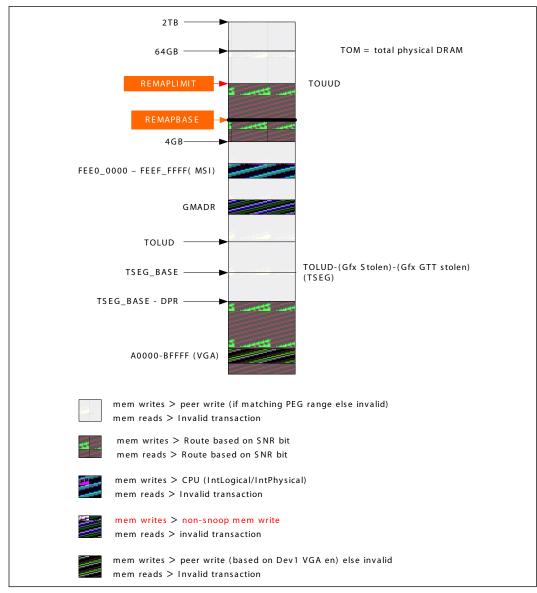

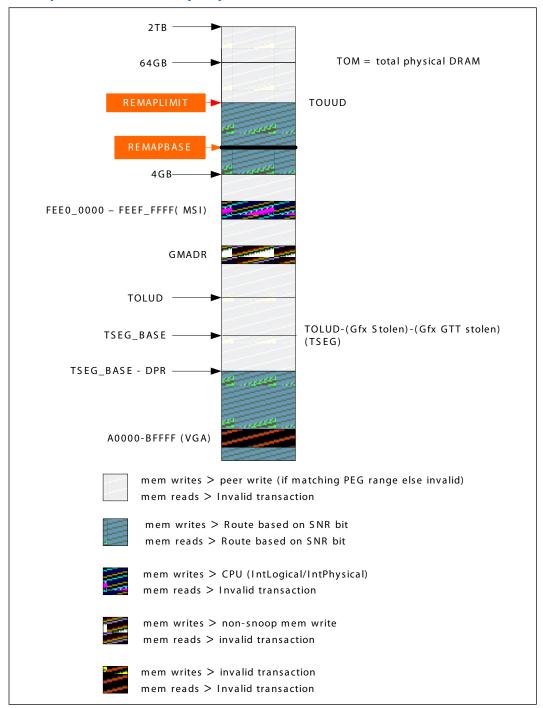

| 2.7 Main Memory Address Space (4 GB to TOUUD)                       |    |

| 2.8 PCI Express* Configuration Address Space                        | 35 |

| 2.9 Graphics Memory Address Ranges                                  |    |

| 2.10 System Management Mode (SMM)                                   |    |

| 2.11 SMM and VGA Access Through GTT TLB                             |    |

| 2.12 Intel® Management Engine (Intel® ME) Stolen Memory Accesses    | 37 |

| 2.13 I/O Address Space                                              | 38 |

| 2.14 Direct Media Interface (DMI) Interface Decode Rules            | 39 |

| 2.15 PCI Express* Interface Decode Rules                            | 41 |

| 2.16 Legacy VGA and I/O Range Decode Rules                          | 44 |

| 2.17 I/O Mapped Registers                                           | 47 |

| 3.0 Host Bridge/DRAM Registers Summary                              | 48 |

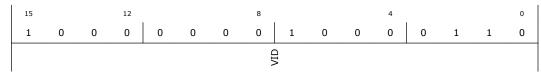

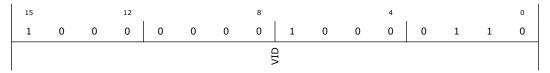

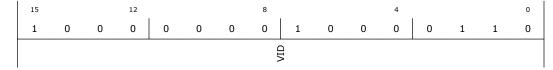

| 3.1 Vendor Identification (VID)—Offset 0h                           | 49 |

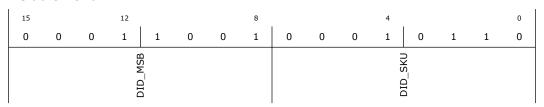

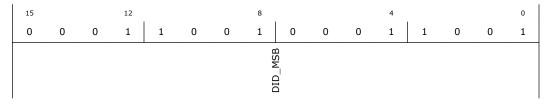

| 3.2 Device Identification (DID)—Offset 2h                           | 49 |

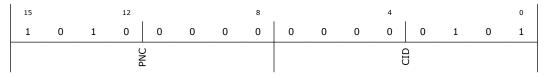

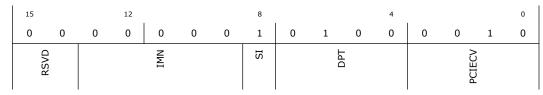

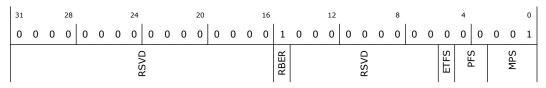

| 3.3 PCI Command (PCICMD)—Offset 4h                                  | 50 |

| 3.4 PCI Status (PCISTS)—Offset 6h                                   | 51 |

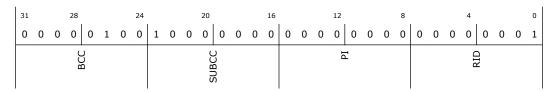

| 3.5 Revision Identification (RID)—Offset 8h                         | 52 |

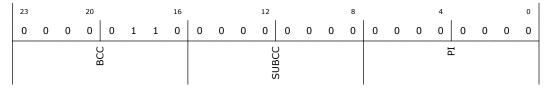

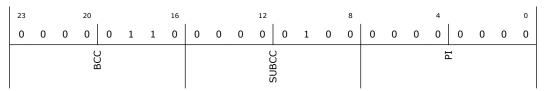

| 3.6 Class Code (CC)—Offset 9h                                       | 53 |

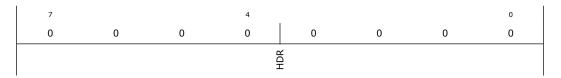

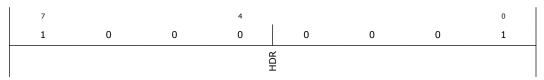

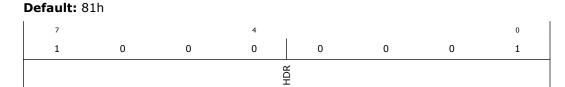

| 3.7 Header Type (HDR)—Offset Eh                                     | 53 |

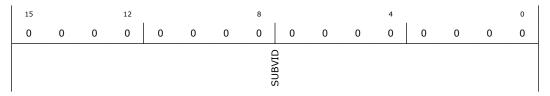

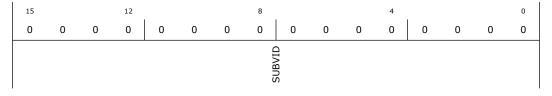

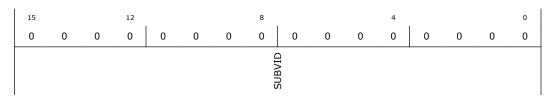

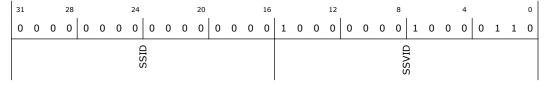

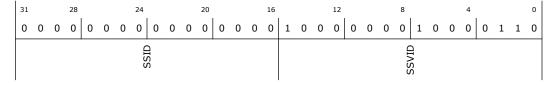

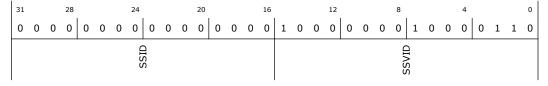

| 3.8 Subsystem Vendor Identification (SVID)—Offset 2Ch               | 54 |

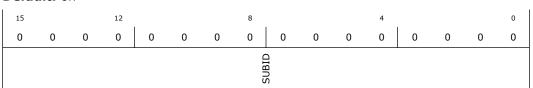

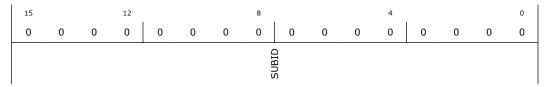

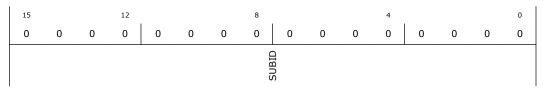

| 3.9 Subsystem Identification (SID)—Offset 2Eh                       | 54 |

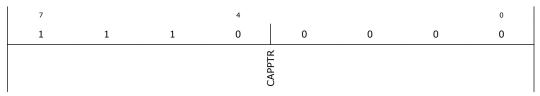

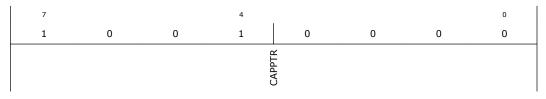

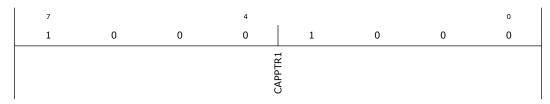

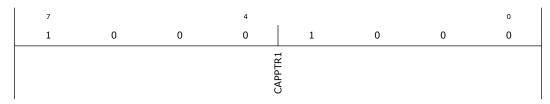

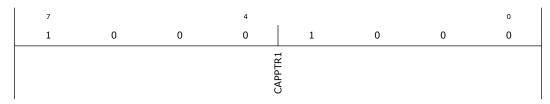

| 3.10 Capabilities Pointer (CAPPTR)—Offset 34h                       | 55 |

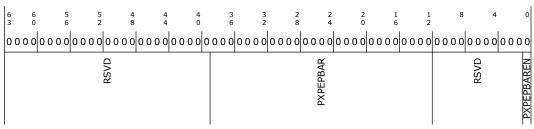

| 3.11 PCI Express Egress Port Base Address (PXPEPBAR)—Offset 40h     | 55 |

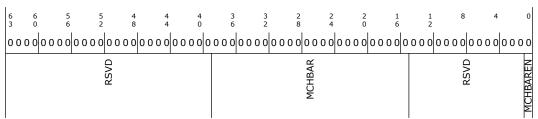

| 3.12 Host Memory Mapped Register Range Base (MCHBAR)—Offset 48h     | 56 |

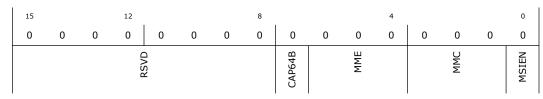

| 3.13 GMCH Graphics Control Register (GGC)—Offset 50h                | 57 |

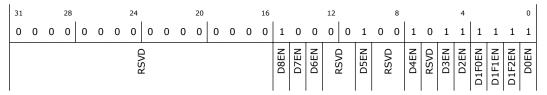

| 3.14 Device Enable (DEVEN)—Offset 54h                               |    |

| 3.15 Protected Audio Video Path Control (PAVPC)—Offset 58h          | 59 |

| 3.16 DMA Protected Range (DPR)—Offset 5Ch                           |    |

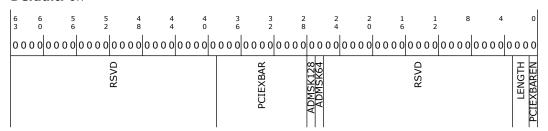

| 3.17 PCI Express Register Range Base Address (PCIEXBAR)—Offset 60h  | 62 |

| 3.18 Root Complex Register Range Base Address (DMIBAR)—Offset 68h   | 63 |

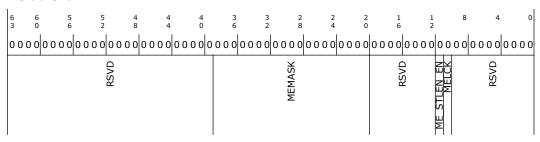

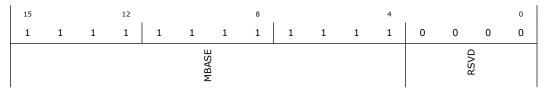

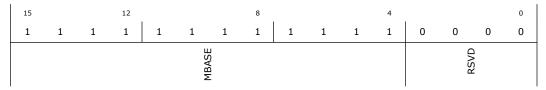

| 3.19 Manageability Engine Base Address Register (MESEG)—Offset 70h  | 64 |

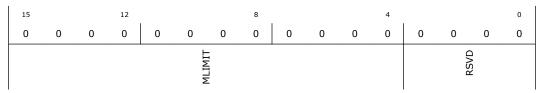

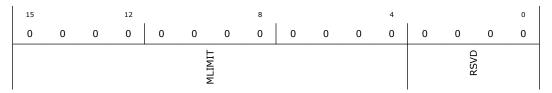

| 3.20 Manageability Engine Limit Address Register (MESEG)—Offset 78h |    |

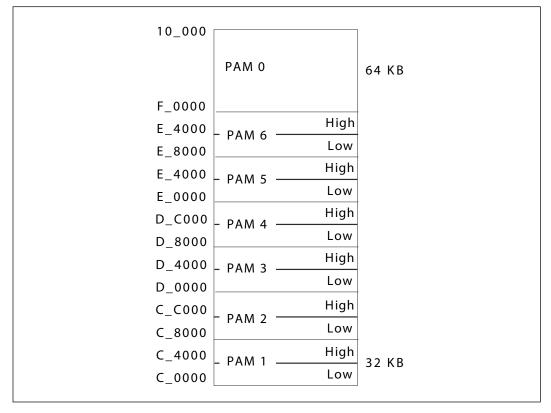

| 3.21 Programmable Attribute Map 0 (PAM0)—Offset 80h                 |    |

| 3.22 Programmable Attribute Map 1 (PAM1)—Offset 81h                 |    |

| 3.23 Programmable Attribute Map 2 (PAM2)—Offset 82h                 |    |

| 3.24 Programmable Attribute Map 3 (PAM3)—Offset 83h                 |    |

| 3.25 Programmable Attribute Map 4 (PAM4)—Offset 84h                 |    |

|       | 3.26 Programmable Attribute Map 5 (PAM5)—Offset 85h                            |      |

|-------|--------------------------------------------------------------------------------|------|

|       | 3.27 Programmable Attribute Map 6 (PAM6)—Offset 86h                            |      |

|       | 3.28 Legacy Access Control (LAC)—Offset 87h                                    |      |

|       | 3.29 System Management RAM Control (SMRAMC)—Offset 88h                         | 75   |

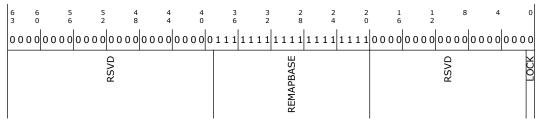

|       | 3.30 Remap Base Address Register (REMAPBASE)—Offset 90h                        | . 76 |

|       | 3.31 Remap Limit Address Register (REMAPLIMIT)—Offset 98h                      | 77   |

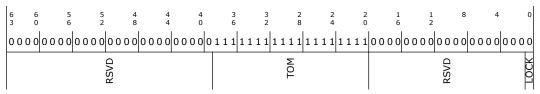

|       | 3.32 Top of Memory (TOM)—Offset A0h                                            | . 77 |

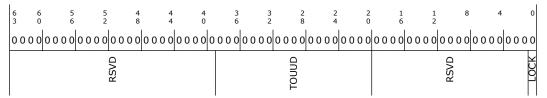

|       | 3.33 Top of Upper Usable DRAM (TOUUD)—Offset A8h                               | . 78 |

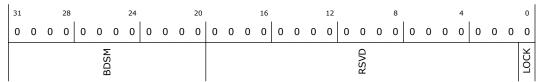

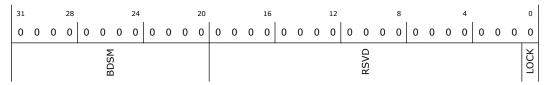

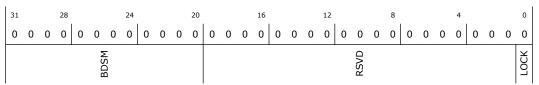

|       | 3.34 Base Data of Stolen Memory (BDSM)—Offset B0h                              | 79   |

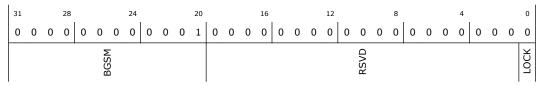

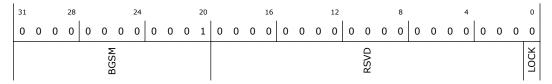

|       | 3.35 Base of GTT stolen Memory (BGSM)—Offset B4h                               |      |

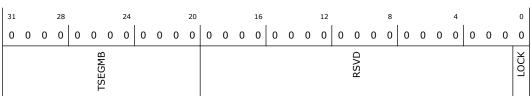

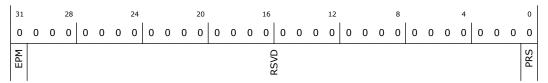

|       | 3.36 TSEG Memory Base (TSEGMB)—Offset B8h                                      |      |

|       | 3.37 Top of Low Usable DRAM (TOLUD)—Offset BCh                                 |      |

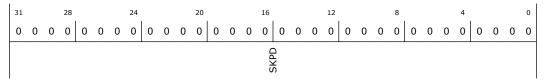

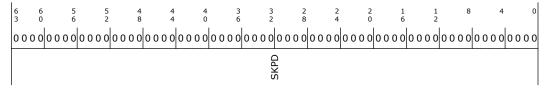

|       | 3.38 Scratchpad Data (SKPD)—Offset DCh                                         |      |

|       | 3.39 Capabilities A (CAPIDO)—Offset E4h                                        |      |

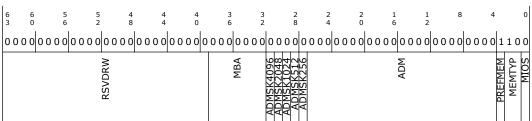

|       | 3.40 Capabilities B (CAPID0)—Offset E8h                                        |      |

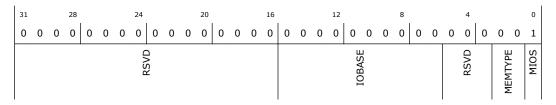

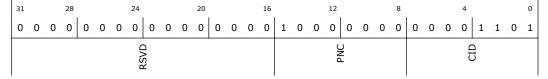

|       | 3.41 Capabilities C (CAPID0)—Offset ECh                                        |      |

|       |                                                                                |      |

| 4.0 1 | ntegrated Graphics Device Registers Summary                                    |      |

|       | 4.1 Vendor Identification (VID2)—Offset 0h                                     |      |

|       | 4.2 Device Identification (DID2)—Offset 2h                                     |      |

|       | 4.3 PCI Command (PCICMD)—Offset 4h                                             |      |

|       | 4.4 PCI Status (PCISTS2)—Offset 6h                                             |      |

|       | 4.5 Revision Identification (RID2)—Offset 8h                                   |      |

|       | 4.6 Class Code (CC)—Offset 9h                                                  |      |

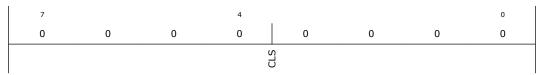

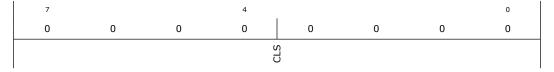

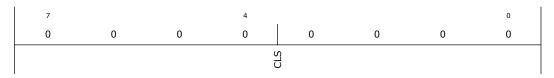

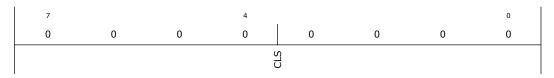

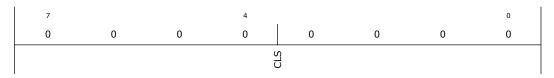

|       | 4.7 Cache Line Size (CLS)—Offset Ch                                            |      |

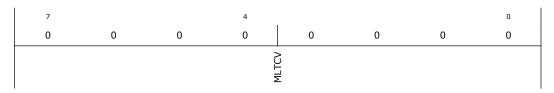

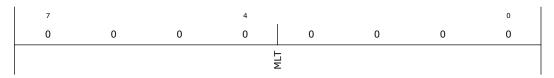

|       | 4.8 Master Latency Timer (MLT2)—Offset Dh                                      |      |

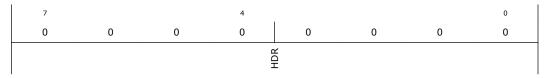

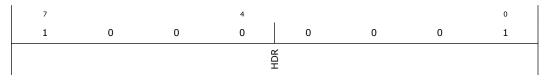

|       | 4.9 Header Type (HDR2)—Offset Eh                                               | 93   |

|       | 4.10 Graphics Translation Table, Memory Mapped Range Address (GTTMMADR)—Offset |      |

|       | 10h                                                                            |      |

|       | 4.11 Graphics Memory Range Address (GMADR)—Offset 18h                          |      |

|       | 4.12 I/O Base Address (IOBAR)—Offset 20h                                       |      |

|       | 4.13 Subsystem Vendor Identification (SVID2)—Offset 2Ch                        |      |

|       | 4.14 Subsystem Identification (SID2)—Offset 2Eh                                |      |

|       | 4.15 Video BIOS ROM Base Address (ROMADR)—Offset 30h                           |      |

|       | 4.16 Capabilities Pointer (CAPPOINT)—Offset 34h                                |      |

|       | 4.17 Interrupt Line (INTRLINE)—Offset 3Ch                                      |      |

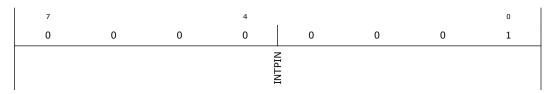

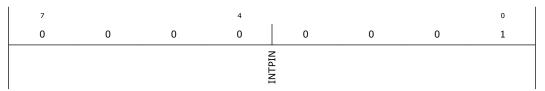

|       | 4.18 Interrupt Pin (INTRPIN)—Offset 3Dh                                        |      |

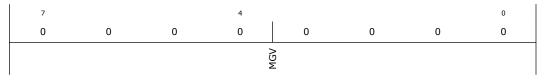

|       | 4.19 Minimum Grant (MINGNT)—Offset 3Eh                                         |      |

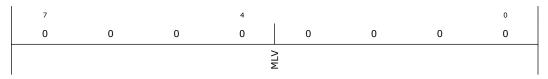

|       | 4.20 Maximum Latency (MAXLAT)—Offset 3Fh                                       |      |

|       | 4.21 Capabilities A (CAPID0)—Offset 44h                                        |      |

|       | 4.22 Capabilities B (CAPID0)—Offset 48h                                        |      |

|       | 4.23 Device Enable (DEVEN0)—Offset 54h                                         |      |

|       | 4.24 Base Data of Stolen Memory (BDSM)—Offset 5Ch                              |      |

|       | 4.25 Multi Size Aperture Control (MSAC)—Offset 62h                             |      |

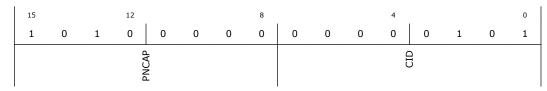

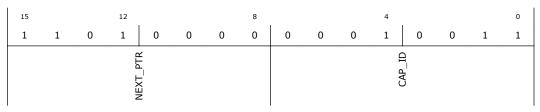

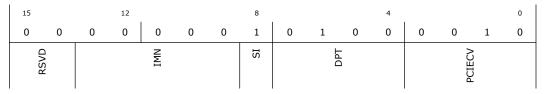

|       | 4.26 PCI Express Capability Header (PCIECAPHDR)—Offset 70h                     |      |

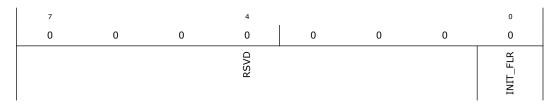

|       | 4.27 Message Signaled Interrupts Capability ID (MSI)—Offset ACh                |      |

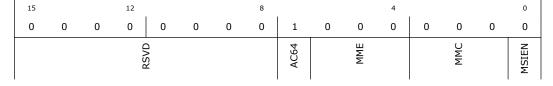

|       | 4.28 Message Control (MC)—Offset AEh                                           | 107  |

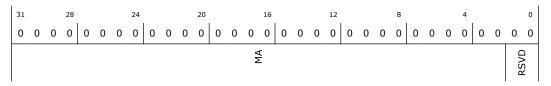

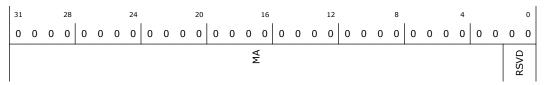

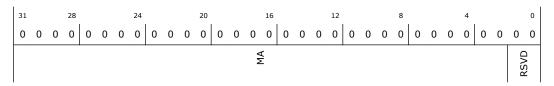

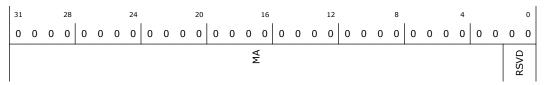

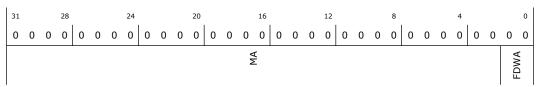

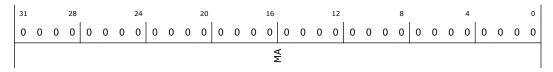

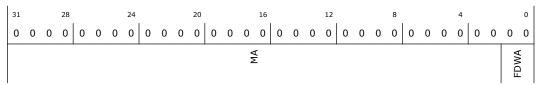

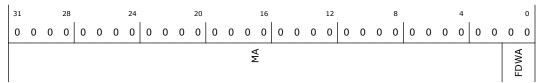

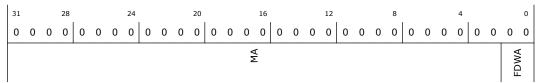

|       | 4.29 Message Address (MA)—Offset B0h                                           |      |

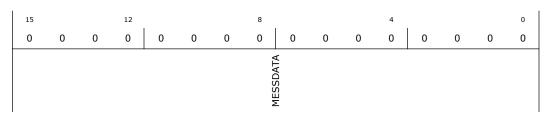

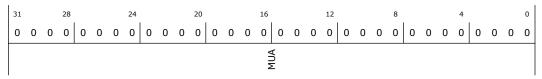

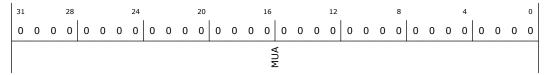

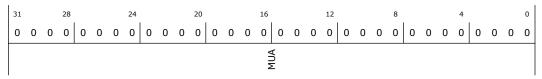

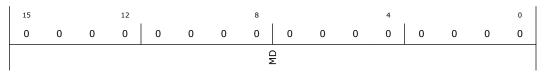

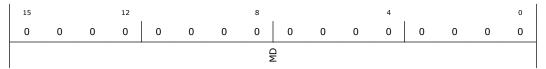

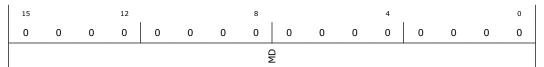

|       | 4.30 Message Data (MD)—Offset B4h                                              |      |

|       | 4.31 Power Management Capabilities ID (PMCAPID)—Offset D0h                     | 109  |

|       | 4.32 Power Management Capabilities (PMCAP)—Offset D2h                          |      |

|       |                                                                                |      |

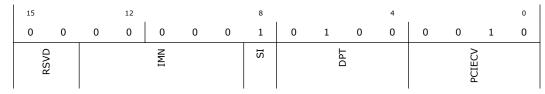

| 4.33 Power Management Control/Status (PMCS)—Offset D4h           | 110 |

|------------------------------------------------------------------|-----|

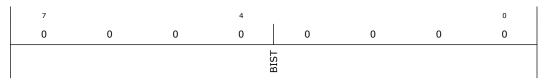

| 5.0 Camarillo Registers Summary                                  | 112 |

| 5.1 Device Enable (DEVEN)—Offset 54h                             | 112 |

| 5.2 Capabilities A (CAPID0)—Offset E4h                           | 113 |

| 5.3 Capabilities B (CAPIDO)—Offset E8h                           |     |

| 6.0 DMIBAR Registers Summary                                     | 117 |

| 6.1 DMI Virtual Channel Enhanced Capability (DMIVCECH)—Offset 0h |     |

| 6.2 DMI Port VC Capability Register 1 (DMIPVCCAP1)—Offset 4h     |     |

| 6.3 DMI Port VC Capability Register 1 (DMIPVCCAP1)—Offset 8h     |     |

| 6.4 DMI Port VC Capability Register 2 (DMI) VCCA(2)—Offset off   |     |

| 6.5 DMI VC0 Resource Capability (DMIVC0RCAP)—Offset 10h          |     |

| 6.6 DMI VC0 Resource Control (DMIVC0RCTL)—Offset 14h             |     |

| 6.7 DMI VC0 Resource Status (DMIVC0RSTS)—Offset 1Ah              |     |

| 6.8 DMI VC1 Resource Capability (DMIVC1RCAP)—Offset 1Ch          |     |

| 6.9 DMI VC1 Resource Control (DMIVC1RCTL)—Offset 20h             |     |

| 6.10 DMI VC1 Resource Status (DMIVC1RSTS)—Offset 26h             |     |

| 6.11 DMI VCm Resource Capability (DMIVCMRCAP)—Offset 34h         |     |

| 6.12 DMI VCm Resource Control (DMIVCMRCTL)—Offset 38h            |     |

| 6.13 DMI VCm Resource Status (DMIVCMRSTS)—Offset 3Eh             |     |

| 6.14 DMI Root Complex Link Declaration (DMIRCLDECH)—Offset 40h   | 127 |

| 6.15 DMI Element Self Description (DMIESD)—Offset 44h            | 128 |

| 6.16 DMI Link Entry 1 Description (DMILE1D)—Offset 50h           | 128 |

| 6.17 DMI Link Entry 1 Address (DMILE1A)—Offset 58h               | 129 |

| 6.18 DMI Link Upper Entry 1 Address (DMILUE1A)—Offset 5Ch        | 130 |

| 6.19 DMI Link Entry 2 Description (DMILE2D)—Offset 60h           |     |

| 6.20 DMI Link Entry 2 Address (DMILE2A)—Offset 68h               |     |

| 6.21 Link Capabilities (LCAP)—Offset 84h                         |     |

| 6.22 Link Control (LCTL)—Offset 88h                              |     |

| 6.23 DMI Link Status (LSTS)—Offset 8Ah                           |     |

| 6.24 Link Control 2 (LCTL2)—Offset 98h                           |     |

| 6.25 Link Status 2 (LSTS2)—Offset 9Ah                            |     |

| 6.26 DMI Uncorrectable Error Status (DMIUESTS)—Offset 1C4h       |     |

| 6.27 DMI Uncorrectable Error Mask (DMIUEMSK)—Offset 1C8h         |     |

| 6.28 DMI Uncorrectable Error Severity (DMIUESEV)—Offset 1CCh     |     |

| 6.29 DMI Correctable Error Status (DMICESTS)—Offset 1D0h         |     |

| 6.30 DMI Correctable Error Mask (DMICEMSK)—Offset 1D4h           |     |

| 7.0 MCHBAR Registers Summary                                     |     |

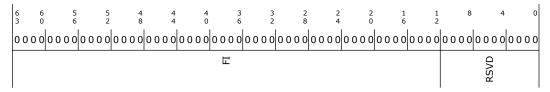

| 7.1 MCHBAR_CH0_CR_TC_PRE_0_0_0_MCHBAR—Offset 4000h               |     |

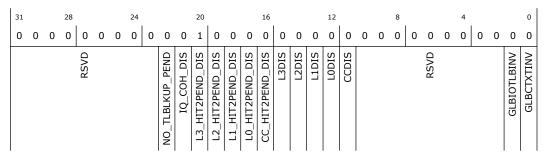

| 7.2 MCHBAR_CH0_CR_SC_GS_CFG_0_0_0_MCHBAR—Offset 401Ch            |     |

| 7.3 MCHBAR_CH0_CR_TC_ODT_0_0_0_MCHBAR—Offset 4070h               |     |

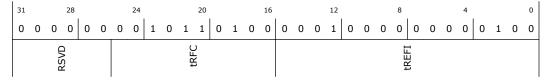

| 7.4 Refresh parameters (TC)—Offset 4238h                         |     |

| 7.5 Refresh timing parameters (TC)—Offset 423Ch                  |     |

| 7.6 Power Management DIMM Idle Energy (PM)—Offset 4260h          |     |

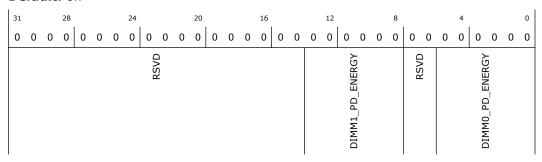

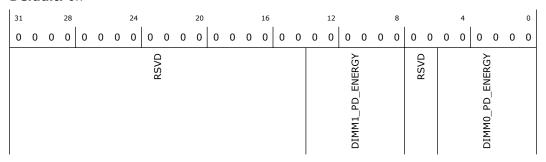

| 7.7 Power Management DIMM Power Down Energy (PM)—Offset 4264h    |     |

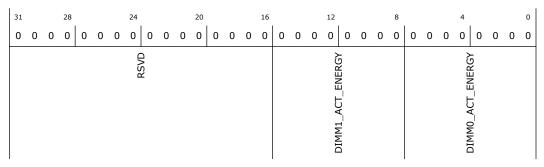

| 7.8 Power Management DIMM Activate Energy (PM)—Offset 4268h      |     |

| 7.9 Power Management DIMM RdCas Energy (PM)—Offset 426Ch         |     |

| 7.10 Power Management DIMM WrCas Energy (PM)—Offset 4270h        |     |

| 7.11 MCHBAR_CH1_CR_TC_PRE_0_0_0_MCHBAR—Offset 4400h              |     |

| 7.12 MCHBAR_CH0_CR_SC_GS_CFG_0_0_0_MCHBAR—Offset 441Ch           | 154 |

|      | MCHBAR_CH0_CR_TC_ODT_0_0_0_MCHBAR—Offset 4470h                           |     |

|------|--------------------------------------------------------------------------|-----|

| 7.14 | Refresh parameters (TC)—Offset 4638h                                     | 157 |

| 7.15 | Refresh timing parameters (TC)—Offset 463Ch                              | 158 |

| 7.16 | Power Management DIMM Idle Energy (PM)—Offset 4660h                      | 158 |

| 7.17 | Power Management DIMM Power Down Energy (PM)—Offset 4664h                | 159 |

| 7.18 | Power Management DIMM Activate Energy (PM)—Offset 4668h                  | 160 |

|      | Power Management DIMM RdCas Energy (PM)—Offset 466Ch                     |     |

|      | Power Management DIMM WrCas Energy (PM)—Offset 4670h                     |     |

|      | MCSCHEDS_CR_SC_GS_CFG_0_0_MCHBAR—Offset 4C1Ch                            |     |

|      | PM—Offset 4C40h                                                          |     |

|      | MCSCHEDS_CR_TC_ODT_0_0_0_MCHBAR—Offset 4C70h                             |     |

|      | Refresh parameters (TC)—Offset 4E38h                                     |     |

| 7.27 | Refresh timing parameters (TC)—Offset 4E3Ch                              | 165 |

|      | Power Management DIMM Idle Energy (PM)—Offset 4E60h                      |     |

| 7.20 | Power Management DIMM Power Down Energy (PM)—Offset 4E64h                | 166 |

|      | Power Management DIMM Activate Energy (PM)—Offset 4E68h                  |     |

|      | Power Management DIMM RdCas Energy (PM)—Offset 4E6Ch                     |     |

|      |                                                                          |     |

|      | Power Management DIMM WrCas Energy (PM)—Offset 4E70h                     |     |

|      | Address decoder inter channel configuration register. (MAD)—Offset 5000h |     |

|      | Address decoder intra channel configuration register. (MAD)—Offset 5004h |     |

|      | Address decoder intra channel configuration register. (MAD)—Offset 5008h |     |

|      | Address decode DIMM parameters. (MAD)—Offset 500Ch                       |     |

|      | Address decode DIMM parameters. (MAD)—Offset 5010h                       |     |

|      | MCDECS_CR_MRC_REVISION_0_0_0_MCHBAR_MCMAIN—Offset 5034h                  |     |

|      | Request count from GT (DRAM)—Offset 5040h                                |     |

|      | Request count from IA (DRAM)—Offset 5044h                                |     |

|      | Request count from IO (DRAM)—Offset 5048h                                |     |

|      | RD data count (DRAM)—Offset 5050h                                        |     |

|      | WR data count (DRAM)—Offset 5054h                                        |     |

|      | Self refresh config. register (PM)—Offset 5060h                          |     |

|      | NCDECS_CR_GFXVTBAR_0_0_0_MCHBAR_NCU—Offset 5400h                         |     |

|      | NCDECS_CR_VTDPVC0BAR_0_0_0_MCHBAR_NCU—Offset 5410h                       |     |

|      | PACKAGE—Offset 5820h                                                     |     |

| 7.46 | PKG-Offset 5828h                                                         | 181 |

|      | PKG-Offset 5830h                                                         |     |

|      | PKG-Offset 5838h                                                         |     |

| 7.49 | PKG-Offset 5840h                                                         | 182 |

| 7.50 | PKG-Offset 5848h                                                         | 182 |

| 7.51 | PKG-Offset 5858h                                                         | 183 |

| 7.52 | DDR-Offset 5880h                                                         | 183 |

| 7.53 | DRAM-Offset 5884h                                                        | 185 |

| 7.54 | DRAM-Offset 5888h                                                        | 186 |

|      | DDR-Offset 588Ch                                                         |     |

|      | DDR-Offset 5890h                                                         |     |

|      | DDR-Offset 5894h                                                         |     |

|      | DDR-Offset 5898h                                                         |     |

|      | DDR-Offset 589Ch.                                                        |     |

|      | DDR-Offset 58A0h.                                                        |     |

|      | PACKAGE—Offset 58A8h                                                     |     |

|      | DDR—Offset 58B0h                                                         |     |

|      |                                                                          | 102 |

|       | 7.64 DDR—Offset 58C0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|       | 7.65 DDR—Offset 58C8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.66 DDR—Offset 58D0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.67 DDR—Offset 58D4h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.68 DDR—Offset 58D8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.69 DDR—Offset 58DCh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.70 PACKAGE—Offset 58F0h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

|       | 7.71 IA—Offset 58FCh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|       | 7.72 GT—Offset 5900h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|       | 7.74 GT—Offset 5948h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|       | 7.75 EDRAM—Offset 594Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

|       | 7.76 Package—Offset 594ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                   |

|       | 7.77 PP0—Offset 5976h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.78 PP1—Offset 5980h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

|       | 7.79 RP—Offset 5994h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|       | 7.80 RP—Offset 5998h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

|       | 7.81 SSKPD—Offset 5D10h.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|       | 7.82 BIOS—Offset 5DA8h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                   |

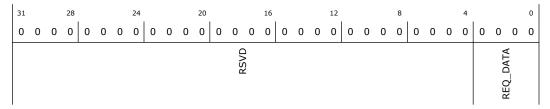

|       | 7.83 PCU_CR_MC_BIOS_REQ_0_0_0_MCHBAR_PCU—Offset 5E00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                   |

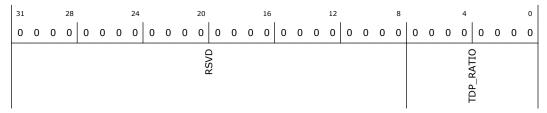

|       | 7.84 CONFIG—Offset 5F3Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

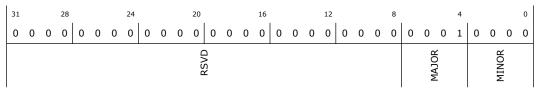

|       | 7.85 CONFIG—Offset 5F40h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|       | 7.86 CONFIG—Offset 5F48h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|       | 7.87 CONFIG—Offset 5F50h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

|       | 7.88 TURBO—Offset 5F54h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                   |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|       | 7.89 Package Thermal Camarillo Status (PKG)—Offset 6200h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 211                                                                                                                               |

|       | 7.89 Package Thermal Camarillo Status (PKG)—Offset 6200h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212                                                                                                                               |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br><b>215</b>                                                                                                                 |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br><b>215</b><br>216                                                                                                          |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br><b>215</b><br>216<br>216                                                                                                   |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br><b>215</b><br>216<br>216<br>219                                                                                            |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br>215<br>216<br>216<br>219<br>221                                                                                            |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br>215<br>216<br>216<br>219<br>221<br>223                                                                                     |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br>215<br>216<br>216<br>219<br>221<br>223<br>224                                                                              |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h <b>FXVTBAR Registers Summary</b> 8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 212<br>215<br>216<br>216<br>219<br>221<br>223<br>224<br>225                                                                       |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h  FXVTBAR Registers Summary  8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h  8.8 Fault Status Register (FSTS)—Offset 34h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 212<br>215<br>216<br>216<br>219<br>221<br>223<br>224<br>225<br>227                                                                |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h <b>FXVTBAR Registers Summary</b> 8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 212<br>215<br>216<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228                                                         |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h  FXVTBAR Registers Summary  8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h  8.8 Fault Status Register (FSTS)—Offset 34h  8.9 Fault Event Control Register (FECTL)—Offset 38h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 212<br>215<br>216<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229                                                  |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h.  FXVTBAR Registers Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229                                                         |

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h  FXVTBAR Registers Summary  8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h  8.8 Fault Status Register (FSTS)—Offset 34h  8.9 Fault Event Control Register (FECTL)—Offset 38h  8.10 Fault Event Data Register (FEDATA)—Offset 3Ch  8.11 Fault Event Address Register (FEADDR)—Offset 40h                                                                                                                                                                                                                                                                                                                                                                                                                                    | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229<br>229<br>230                                           |

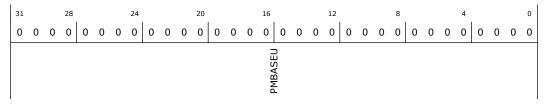

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h  FXVTBAR Registers Summary  8.1 Version Register (VER)—Offset 0h  8.2 Capability Register (CAP)—Offset 8h  8.3 Extended Capability Register (ECAP)—Offset 10h  8.4 Global Command Register (GCMD)—Offset 18h  8.5 Global Status Register (GSTS)—Offset 1Ch  8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h  8.7 Context Command Register (CCMD)—Offset 28h  8.8 Fault Status Register (FSTS)—Offset 34h  8.9 Fault Event Control Register (FECTL)—Offset 38h  8.10 Fault Event Data Register (FEDATA)—Offset 3Ch  8.11 Fault Event Address Register (FEDATA)—Offset 40h  8.12 Fault Event Upper Address Register (FEUADDR)—Offset 44h                                                                                                                                                                                                                                                                                                                                                                      | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229<br>230<br>230                                           |

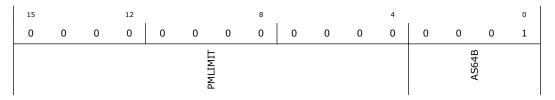

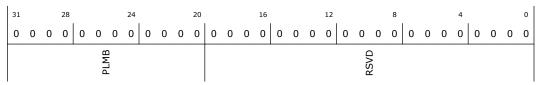

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h  8.1 Version Register (VER)—Offset 0h 8.2 Capability Register (CAP)—Offset 8h 8.3 Extended Capability Register (ECAP)—Offset 10h 8.4 Global Command Register (GCMD)—Offset 18h 8.5 Global Status Register (GSTS)—Offset 1Ch 8.6 Root-Entry Table Address Register (RTADDR)—Offset 20h 8.7 Context Command Register (CCMD)—Offset 28h 8.8 Fault Status Register (FSTS)—Offset 34h 8.9 Fault Event Control Register (FECTL)—Offset 38h 8.10 Fault Event Data Register (FEDATA)—Offset 3Ch 8.11 Fault Event Address Register (FEADDR)—Offset 40h 8.12 Fault Event Upper Address Register (FEUADDR)—Offset 44h 8.13 Advanced Fault Log Register (AFLOG)—Offset 58h 8.14 Protected Memory Enable Register (PMEN)—Offset 64h 8.15 Protected Low-Memory Base Register (PLMBASE)—Offset 68h                                                                                                                                                                                                                                   | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229<br>230<br>230<br>231<br>232                             |

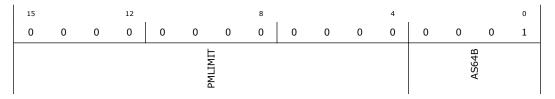

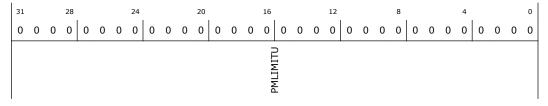

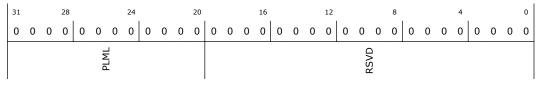

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229<br>230<br>231<br>232<br>233                             |

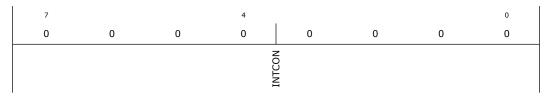

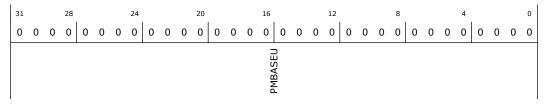

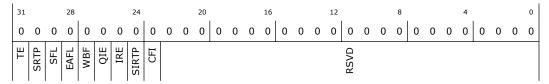

| 8.0 G | 7.90 Memory Thermal Camarillo Status (DDR)—Offset 6204h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 212<br>215<br>216<br>219<br>221<br>223<br>224<br>225<br>227<br>228<br>229<br>230<br>231<br>232<br>233<br>234                      |